| Re: [hatari-devel] DSP for Previous |

[ Thread Index | Date Index | More lists.tuxfamily.org/hatari-devel Archives ]

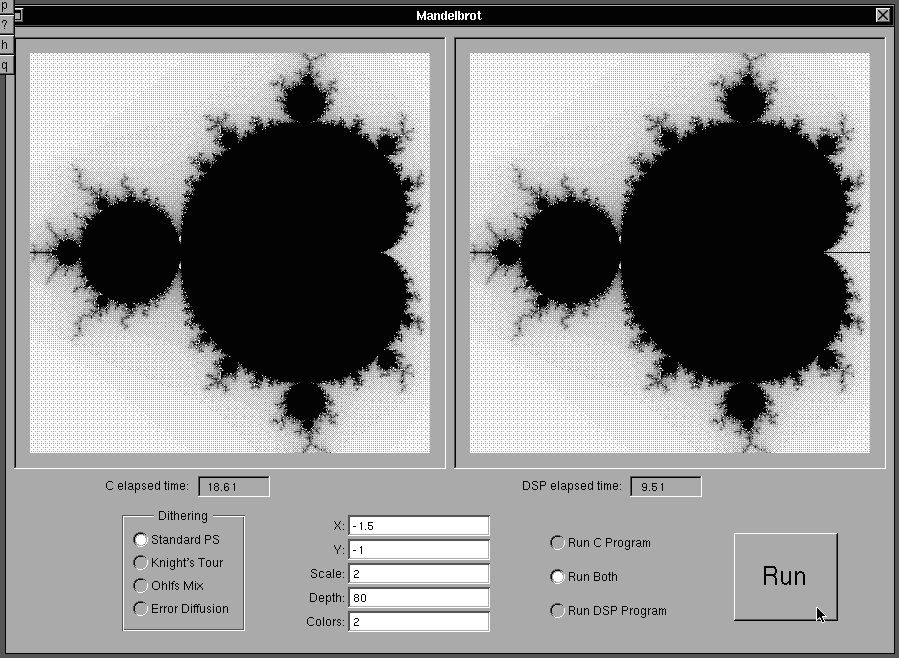

Am 11.06.2015 um 23:21 schrieb Nicolas Pomarède <npomarede@xxxxxxxxxxxx>: > Le 11/06/2015 23:08, Andreas Grabher a écrit : >> You're welcome! I found some more problems. But now it seems that the >> DSP works for me! >> >> Most problems i found were related to the interrupt system. It does not >> reflect real behavior. I think i found most issues, but with this method >> of doing interrupts we will run into further problems sooner or later. I >> think it needs to be rewritten. My current patch is just a workaround. >> >> Now it works like this: >> The device sends the interrupt to the DSP like some kind of message. If >> it is not masked, it is then added to a list. The DSP reads the >> interrupt from the list, removes it and executes the interrupt service >> routine. If a masked interrupt is unmasked, the interrupt message needs >> to be re-sent. If an interrupt is on the list while it gets masked, it >> needs to be removed from the list. If the service routine does not make >> the device release the interrupt on first try, it needs to be sent >> again, if it isn't masked. >> >> How it should work: >> The device asserts the interrupt line. The DSP samples the line and sees >> the interrupt, if it is not masked. It executes the service routine, >> which then makes the device release the interrupt line. If a masked >> interrupt is unmasked, the DSP will start seeing it. If a pending >> interrupt is masked, the DSP will no longer see it. If the service >> routine does not make the device release the interrupt, the DSP will >> keep on seeing it, unless it is masked. >> > > > Hi > > thanks for your patch ; regarding changing the interrupt behaviour, the current one might not be complete, but it seems it doesn't cause failure so far (because demos/programs don't rely on it), so I think we should wait after 1.9 is released before doing big changes in Hatari. > > But we certainly need to handle it by having a pending and a mask registers (as for the 680xx), not temporarily as a list ; better go for the good way to handle it, instead of having an intermediate one with lists (and handling mask/pending is in fact much simpler than handling lists of events, resending events, ...) > > As for the rest, I think Laurent knows the DSP better than I do :) > > Nicolas > I see! I also would not change it, if it worked for me ;-) But in case you want to apply the changes anyway, i appended another little patch. Again this needs to be added manually, as our versions are drifting away. It might be easier to just wait until i'm done and then merge. In the meantime i tested some things and it seems to work quite well. I love to finally hear sound playing! But while testing i may have found another bug. This time it may be in the DSP logic itself. If you look at the appended screenshot of a Mandelbrot application you may notice a black line in the middle (vertically) of the DSP (right) window. I can't test on real hardware, but i don't think it should be there. I tried to get some useful debugging output and think i have copied 2 full loops of what it does. The output is in the appended Mandelbrot debug text. Maybe someone used to the DSP can see an instruction in the loop that may be responsible for this. Then i think it will be easy to fix.

Attachment:

dsp_patch14.diff

Description: Binary data

p:0092 208541 (02 cyc) tfr x0,a x0,x1 Reg: x1 $b47ae2 -> $b4ccce Reg: a $00:000002:000000 -> $ff:b4ccce:000000 p:0093 20c759 (02 cyc) tfr y0,b y0,y1 Reg: b $01:000000:000000 -> $ff:c5c290:000000 p:0094 06d500 0000a7 (06 cyc) do r5,p:$00a7 Reg: sp $02 -> $04 Reg: ssh $8f -> $96 Reg: ssl $10 -> $8050 Reg: la $00a9 -> $00a7 Reg: lc $02df -> $0050 p:0096 21c498 (02 cyc) mpy +y0,y0,b a,x0 Reg: b $ff:c5c290:000000 -> $00:1a7fca:fd2200 p:0097 200080 (02 cyc) mpy +x0,x0,a Reg: a $ff:b4ccce:000000 -> $00:2c2e13:11eb88 p:0098 200018 (02 cyc) add a,b Reg: b $00:1a7fca:fd2200 -> $00:46adde:0f0d88 Reg: sr $8050 -> $8040 p:0099 0af0a5 0000a1 (06 cyc) jec p:$00a1 p:00a1 2000d8 (02 cyc) mpy +y0,x0,b Reg: b $00:46adde:0f0d88 -> $00:22374a:da9fc0 Reg: sr $8040 -> $8050 p:00a2 20003a (02 cyc) asl b Reg: b $00:22374a:da9fc0 -> $00:446e95:b53f80 Reg: sr $8050 -> $8040 p:00a3 20003a (02 cyc) asl b Reg: b $00:446e95:b53f80 -> $00:88dd2b:6a7f00 Reg: sr $8040 -> $8060 p:00a4 200078 (02 cyc) add y1,b Reg: b $00:88dd2b:6a7f00 -> $00:4e9fbb:6a7f00 Reg: sr $8060 -> $8041 p:00a5 21e696 (02 cyc) mac -y0,y0,a b,y0 Reg: y0 $c5c290 -> $4e9fbb Reg: a $00:2c2e13:11eb88 -> $00:11ae48:14c988 Reg: sr $8041 -> $8051 p:00a6 200032 (02 cyc) asl a Reg: a $00:11ae48:14c988 -> $00:235c90:299310 Reg: sr $8051 -> $8050 p:00a7 200060 (02 cyc) add x1,a Reg: a $00:235c90:299310 -> $ff:d8295e:299310 Reg: sr $8050 -> $8058 p:0096 21c498 (02 cyc) mpy +y0,y0,b a,x0 Reg: x0 $b4ccce -> $d8295e Reg: b $00:4e9fbb:6a7f00 -> $00:304b73:3ba532 Reg: sr $8058 -> $8050 p:0097 200080 (02 cyc) mpy +x0,x0,a Reg: a $ff:d8295e:299310 -> $00:0c6632:9e7d08 p:0098 200018 (02 cyc) add a,b Reg: b $00:304b73:3ba532 -> $00:3cb1a5:da223a p:0099 0af0a5 0000a1 (06 cyc) jec p:$00a1 p:00a1 2000d8 (02 cyc) mpy +y0,x0,b Reg: b $00:3cb1a5:da223a -> $ff:e7877e:773354 Reg: sr $8050 -> $8058 p:00a2 20003a (02 cyc) asl b Reg: b $ff:e7877e:773354 -> $ff:cf0efc:ee66a8 Reg: sr $8058 -> $8059 p:00a3 20003a (02 cyc) asl b Reg: b $ff:cf0efc:ee66a8 -> $ff:9e1df9:dccd50 Reg: sr $8059 -> $8049 p:00a4 200078 (02 cyc) add y1,b Reg: b $ff:9e1df9:dccd50 -> $ff:63e089:dccd50 Reg: sr $8049 -> $8069 p:00a5 21e696 (02 cyc) mac -y0,y0,a b,y0 Reg: y0 $4e9fbb -> $800000 Reg: a $00:0c6632:9e7d08 -> $ff:dc1abf:62d7d6 Reg: sr $8069 -> $8059 p:00a6 200032 (02 cyc) asl a Reg: a $ff:dc1abf:62d7d6 -> $ff:b8357e:c5afac Reg: sr $8059 -> $8049 p:00a7 200060 (02 cyc) add x1,a Reg: a $ff:b8357e:c5afac -> $ff:6d024c:c5afac Reg: sr $8049 -> $8069 p:0096 21c498 (02 cyc) mpy +y0,y0,b a,x0 Reg: x0 $d8295e -> $800000 Reg: b $ff:63e089:dccd50 -> $00:800000:000000 Reg: sr $8069 -> $8061 p:0097 200080 (02 cyc) mpy +x0,x0,a Reg: a $ff:6d024c:c5afac -> $00:800000:000000 p:0098 200018 (02 cyc) add a,b Reg: b $00:800000:000000 -> $01:000000:000000 Reg: sr $8061 -> $8070 p:0099 0af0a5 0000a1 (06 cyc) jec p:$00a1 p:009b 22ae00 (02 cyc) move r5,a Reg: a $00:800000:000000 -> $00:000050:000000 p:009c 0444bf (02 cyc) movec lc,x0 Reg: x0 $800000 -> $00004e p:009d 200044 (02 cyc) sub x0,a Reg: a $00:000050:000000 -> $00:000002:000000 Reg: sr $8070 -> $8050 p:009e 00008c (02 cyc) enddo Reg: sp $04 -> $02 Reg: ssh $96 -> $8f Reg: ssl $8050 -> $10 Reg: la $00a7 -> $00a9 Reg: lc $004e -> $02df p:009f 0af080 0000a9 (06 cyc) jmp p:$00a9 p:00a9 564e00 (02 cyc) move a,x:(r6)+n6 Reg: r6 $2fe1 -> $2fe2 Mem: x:0x2fe1 0x000002 -> 0x000002 p:008f 44d900 (02 cyc) move x:(r1)+,x0 Reg: x0 $00004e -> $b51eb9 Reg: r1 $26c4 -> $26c5 p:0090 46d100 (02 cyc) move x:(r1)-,y0 Reg: y0 $800000 -> $c5c290 Reg: r1 $26c5 -> $26c4 p:0091 044911 (04 cyc) lua (r1)+n1,r1 Reg: r1 $26c4 -> $26c6 p:0092 208541 (02 cyc) tfr x0,a x0,x1 Reg: x1 $b4ccce -> $b51eb9 Reg: a $00:000002:000000 -> $ff:b51eb9:000000 p:0093 20c759 (02 cyc) tfr y0,b y0,y1 Reg: b $01:000000:000000 -> $ff:c5c290:000000 p:0094 06d500 0000a7 (06 cyc) do r5,p:$00a7 Reg: sp $02 -> $04 Reg: ssh $8f -> $96 Reg: ssl $10 -> $8050 Reg: la $00a9 -> $00a7 Reg: lc $02de -> $0050 p:0096 21c498 (02 cyc) mpy +y0,y0,b a,x0 Reg: b $ff:c5c290:000000 -> $00:1a7fca:fd2200 p:0097 200080 (02 cyc) mpy +x0,x0,a Reg: a $ff:b51eb9:000000 -> $00:2bce06:93c362 p:0098 200018 (02 cyc) add a,b Reg: b $00:1a7fca:fd2200 -> $00:464dd1:90e562 Reg: sr $8050 -> $8040 p:0099 0af0a5 0000a1 (06 cyc) jec p:$00a1 p:00a1 2000d8 (02 cyc) mpy +y0,x0,b Reg: b $00:464dd1:90e562 -> $00:221205:0cf420 Reg: sr $8040 -> $8050 p:00a2 20003a (02 cyc) asl b Reg: b $00:221205:0cf420 -> $00:44240a:19e840 Reg: sr $8050 -> $8040 p:00a3 20003a (02 cyc) asl b Reg: b $00:44240a:19e840 -> $00:884814:33d080 Reg: sr $8040 -> $8060 p:00a4 200078 (02 cyc) add y1,b Reg: b $00:884814:33d080 -> $00:4e0aa4:33d080 Reg: sr $8060 -> $8041 p:00a5 21e696 (02 cyc) mac -y0,y0,a b,y0 Reg: y0 $c5c290 -> $4e0aa4 Reg: a $00:2bce06:93c362 -> $00:114e3b:96a162 Reg: sr $8041 -> $8051 p:00a6 200032 (02 cyc) asl a Reg: a $00:114e3b:96a162 -> $00:229c77:2d42c4 Reg: sr $8051 -> $8050 p:00a7 200060 (02 cyc) add x1,a Reg: a $00:229c77:2d42c4 -> $ff:d7bb30:2d42c4 Reg: sr $8050 -> $8058 p:0096 21c498 (02 cyc) mpy +y0,y0,b a,x0 Reg: x0 $b51eb9 -> $d7bb30 Reg: b $00:4e0aa4:33d080 -> $00:2f94f8:c27220 Reg: sr $8058 -> $8050 p:0097 200080 (02 cyc) mpy +x0,x0,a Reg: a $ff:d7bb30:2d42c4 -> $00:0cab26:fe5200 p:0098 200018 (02 cyc) add a,b Reg: b $00:2f94f8:c27220 -> $00:3c401f:c0c420 p:0099 0af0a5 0000a1 (06 cyc) jec p:$00a1 p:00a1 2000d8 (02 cyc) mpy +y0,x0,b Reg: b $00:3c401f:c0c420 -> $ff:e772b8:479580 Reg: sr $8050 -> $8058 p:00a2 20003a (02 cyc) asl b Reg: b $ff:e772b8:479580 -> $ff:cee570:8f2b00 Reg: sr $8058 -> $8059 p:00a3 20003a (02 cyc) asl b Reg: b $ff:cee570:8f2b00 -> $ff:9dcae1:1e5600 Reg: sr $8059 -> $8049 p:00a4 200078 (02 cyc) add y1,b Reg: b $ff:9dcae1:1e5600 -> $ff:638d71:1e5600 Reg: sr $8049 -> $8069 p:00a5 21e696 (02 cyc) mac -y0,y0,a b,y0 Reg: y0 $4e0aa4 -> $800000 Reg: a $00:0cab26:fe5200 -> $ff:dd162e:3bdfe0 Reg: sr $8069 -> $8059 p:00a6 200032 (02 cyc) asl a Reg: a $ff:dd162e:3bdfe0 -> $ff:ba2c5c:77bfc0 Reg: sr $8059 -> $8049 p:00a7 200060 (02 cyc) add x1,a Reg: a $ff:ba2c5c:77bfc0 -> $ff:6f4b15:77bfc0 Reg: sr $8049 -> $8069 p:0096 21c498 (02 cyc) mpy +y0,y0,b a,x0 Reg: x0 $d7bb30 -> $800000 Reg: b $ff:638d71:1e5600 -> $00:800000:000000 Reg: sr $8069 -> $8061 p:0097 200080 (02 cyc) mpy +x0,x0,a Reg: a $ff:6f4b15:77bfc0 -> $00:800000:000000 p:0098 200018 (02 cyc) add a,b Reg: b $00:800000:000000 -> $01:000000:000000 Reg: sr $8061 -> $8070 p:0099 0af0a5 0000a1 (06 cyc) jec p:$00a1 p:009b 22ae00 (02 cyc) move r5,a Reg: a $00:800000:000000 -> $00:000050:000000 p:009c 0444bf (02 cyc) movec lc,x0 Reg: x0 $800000 -> $00004e p:009d 200044 (02 cyc) sub x0,a Reg: a $00:000050:000000 -> $00:000002:000000 Reg: sr $8070 -> $8050 p:009e 00008c (02 cyc) enddo Reg: sp $04 -> $02 Reg: ssh $96 -> $8f Reg: ssl $8050 -> $10 Reg: la $00a7 -> $00a9 Reg: lc $004e -> $02de p:009f 0af080 0000a9 (06 cyc) jmp p:$00a9 p:00a9 564e00 (02 cyc) move a,x:(r6)+n6 Reg: r6 $2fe2 -> $2fe3 Mem: x:0x2fe2 0x000002 -> 0x000002 p:008f 44d900 (02 cyc) move x:(r1)+,x0 Reg: x0 $00004e -> $b570a5 Reg: r1 $26c6 -> $26c7 p:0090 46d100 (02 cyc) move x:(r1)-,y0 Reg: y0 $800000 -> $c5c290 Reg: r1 $26c7 -> $26c6 p:0091 044911 (04 cyc) lua (r1)+n1,r1 Reg: r1 $26c6 -> $26c8 p:0092 208541 (02 cyc) tfr x0,a x0,x1 Reg: x1 $b51eb9 -> $b570a5 Reg: a $00:000002:000000 -> $ff:b570a5:000000 p:0093 20c759 (02 cyc) tfr y0,b y0,y1 Reg: b $01:000000:000000 -> $ff:c5c290:000000 p:0094 06d500 0000a7 (06 cyc) do r5,p:$00a7 Reg: sp $02 -> $04 Reg: ssh $8f -> $96 Reg: ssl $10 -> $8050 Reg: la $00a9 -> $00a7 Reg: lc $02dd -> $0050

| Mail converted by MHonArc 2.6.19+ | http://listengine.tuxfamily.org/ |